## 2024年度 永守財団 研究助成 研究報告書

|             |               |

|-------------|---------------|

| 所 属 機 関     | 大阪大学 大学院工学研究科 |

| 職 位 または 役 職 | 助 教           |

| 氏 名         | 福永 崇平         |

### 1. 研究題目

機電一体型モータに適用するSiCパワーモジュールの高信頼構造設計技術の開発

### 2. 研究目的

モータを駆動するインバータをはじめとした電力変換回路の小型高効率化が求められている。近年注目が集まる炭化ケイ素(SiC)パワーデバイスの特長を活かして、機電一体型モータと呼ばれる、高温となるモータの近傍にインバータを配置することによる電動駆動システムの小型高性能化が検討されている。しかし高温環境下における長期間信頼動作を保証するためには、パワーデバイスだけでなく、これを複数搭載したパワーモジュールの配線構造設計や実装材料の高耐熱化が必要になる。特にSiCパワーモジュールはSiパワーモジュールと比べ、比較的小さいチップを多数実装するマルチチップ構造が検討されている。マルチチップモジュールでは、発熱するチップ間の熱干渉によるジャンクション温度の上昇が問題になる。また実装するパワーデバイスのオン抵抗やゲートしきい値電圧などの電気的特性の違いが引き起こす電流アンバランスによって発熱分布が偏ると、熱応力が集中し、信頼性を著しく低下させる。

本研究では、高温環境下で長期信頼性を担保するためのマルチチップSiCパワーモジュールの構造設計法を開発する。前年の研究助成において、熱干渉は単なるチップ間距離だけではなく、モジュール基板に接合する接合材料(はんだ等)や、基板配線パターン、パッケージ構造など、複数要素の影響を受けることを、過渡熱抵抗測定により明らかにした。本助成では構造パラメータが与える影響を数値モデルに適用し、非線形計画法に基づく構造最適化を行う。最大ジャンクション温度およびモジュール内部の温度勾配による熱応力を目的関数とし、これらを最小化する構造パラメータを算出し、実装したモジュールを評価する。チップ配置や配線構造設計については、数値シミュレーションと実験の両方から検討を進め、妥当性を検証する。これにより安全マージンを高く持った従来の冗長設計ではなく、SiCパワーデバイスの特長を最大限引き出しつつ信頼性を確保可能なモジュール設計法を確立し、パワエレ機器の普及に貢献する。

### 3. 研究内容及び成果

本検討では、構造パラメータの影響を反映したシミュレーションモデルに最適化アルゴリズムを適用することで、パワーモジュール基板の構造設計を行った。モデルベース設計の妥当性を保証するため、過去に検討した金属放熱基板の実験結果をもとに、数値モデルを作成した。SiCショットキーバリアダイオード(SBD)を鉛フリーはんだで実装したサンプルについて、過渡熱抵抗測定の結果からはんだ層の熱抵抗および界面熱抵抗を同定した。また走査型電子顕微鏡(SEM)を用いた断面観察により、実装したサンプルにおける接着層などの厚みを測定した。Femtet(Murata software)を用いて、これらを反映した有限要素法に基づきシミュレーションモデルを作成した。

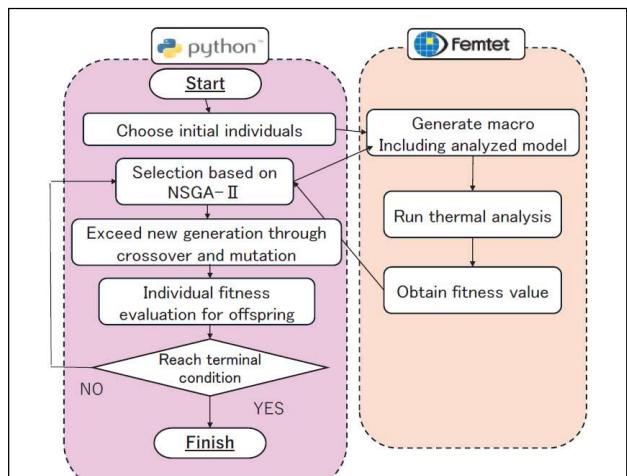

作成したシミュレーションモデルに対して、最適化アルゴリズムに基づくチップ実装位置の多目的最適化を行った。図1は提案する最適設計手法のフローチャートである。提案アルゴリズムはPythonおよびライブラリDEAPにより記述し、Femtetをスクリプトにより制御してシミュレーションを実行する。出力したシミュレーション結果から目的関数値を計算する。本検討ではメタヒューリスティックス手法の1つである遺伝的アルゴリズムのうち、非優越ソートアルゴリズムII(NSGA-II)を用いた多目的最適化を行った。以下では、提案アルゴリズムを用いた設計の一例を示す。

パワーモジュールを構成する接合部(はんだ、モジュール基板の界面等)で生じる熱応力は、温度差 $\Delta T$ に比例する。そこで本検討では、使用時の繰り返し熱応力を低減するために、実装する複数チップの平均温度を下げつつ温度分散を小さくすることで、最大ジャンクション温度を下げる。すなわち、目的関数を以下に設定した。

$$\min. T_{\text{Jave}} = f_1(x_{\text{die}i}, y_{\text{die}i}, W, L) \quad - (1)$$

$$\min. T_{\text{Jvar}} = f_2(x_{\text{die}i}, y_{\text{die}i}, W, L) \quad - (2)$$

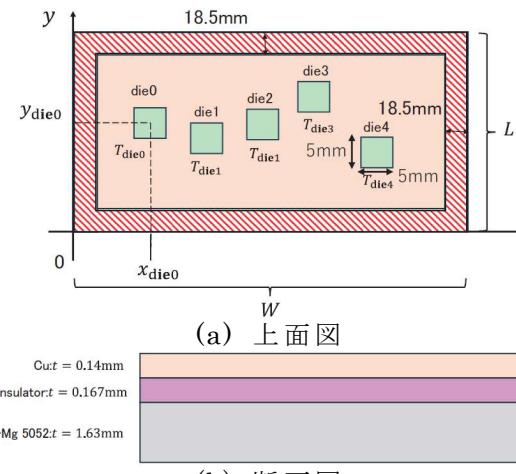

ここで $T_{\text{Jave}}$ ,  $T_{\text{Jvar}}$ はそれぞれ実装した各チップの平均温度、温度分散である。また $x_{\text{die}i}$ ,  $y_{\text{die}i}$ はそれぞれ基板上の*i*番目のチップの中心座標である。 $W$ ,  $L$ はそれぞれモジュール基板の幅、奥行である。図2は検討するモジュール基板の構造である。なおモジュール基板の周辺部(図中の網掛けした領域)に、モジュール実装時のワイヤボンディングおよび配線領域を設けている。

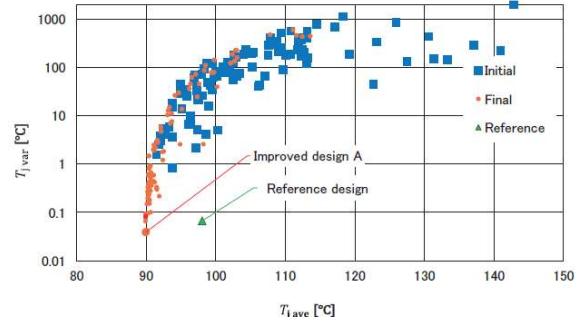

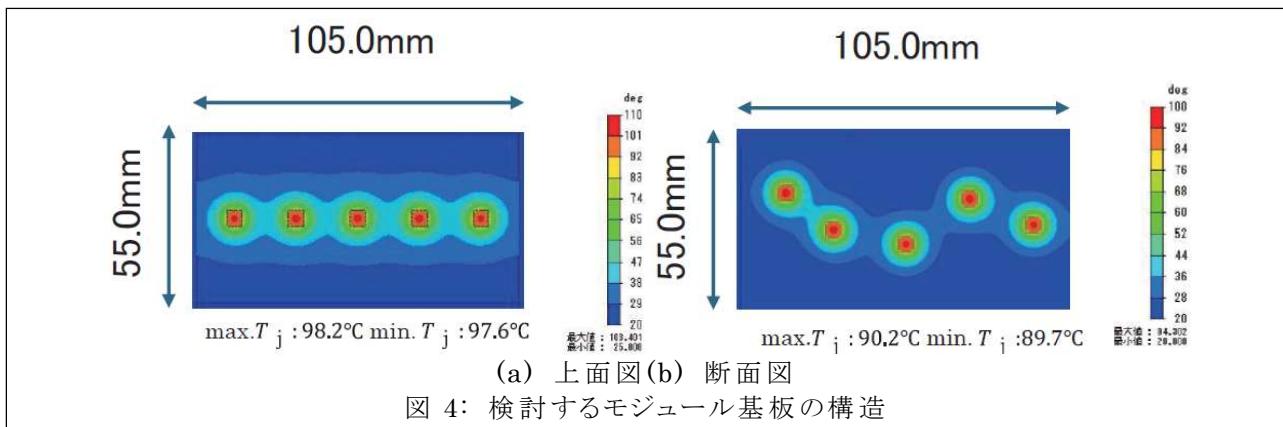

図3は提案アルゴリズムにより多目的最適化した、横軸に5チップの平均温度 $T_{\text{Jave}}[^\circ\text{C}]$ 、縦軸に温度分散 $T_{\text{Jvar}}[^\circ\text{C}]$ をプロットしたものである。ただし青は初期世代、オレンジは最終世代の個体集団を表しており、世代を重ねることで両目的関数が同時に最小化されている。多目的最適化の結果から、レファレンス基板と比較して $T_{\text{Jvar}}$ を抑えつつ $T_{\text{Jave}}$ を低減できるレイアウトをImproved design Aとして選択した。各基板の温度分布のシミュレーション結果を図4に示す。Reference

図1：提案する最適化アルゴリズムのフローチャート

図2：検討するモジュール基板の構造

図3： $T_{\text{Jave}}$ ,  $T_{\text{Jvar}}$ を同時に低減する多目的最適化の実行結果

design と比較して、提案アルゴリズムを適用した Improved design A は、チップを互い違いに配置することで、 $T_{jave}$ と $T_{jvar}$ を低減できる、すなわち基板サイズを制約条件とするとき、チップ配置を最適設計することで基板上の最大温度を下げることができる。これにより熱応力を低減し、高信頼化につなげることができる。

#### 4. 今後の研究の見通し

助成者がこれまでに明らかにした、モジュール基板構造パラメータが放熱特性に与える影響を実験的に評価、および結果を反映した数値モデルを用いて熱応力集中を緩和する最適構造設計を行ったパワーモジュールに対し、連続動作を想定した信頼性試験を行う。SiC MOSFET を実装したパワーモジュールの評価において課題となるバイポーラ通電劣化の影響を受けないパワーサイクル試験システムを開発し、最適設計したパワーモジュールのはんだやワイヤ等の接合部に対する信頼性評価を行い、設計の妥当性を検証する。加えて機電一体型モータへの適用を前提とした、最適設計したパワーモジュールを適用したインバータを設計・作製し、回路連続動作に対するモジュール接合部の信頼性評価を行い、寿命予測を行う。

#### 5. 助成研究による主な発表論文、著書名

##### (1) 査読付き学術論文:

1. S. Fukunaga, and T. Funaki: "Analysis of errors in junction temperature estimated by temperature-sensitive electrical parameter for parallel-connected SBDs," *Jpn. J. Appl. Phys.*, 64, 02SP24, Feb. 2025.

2. S. Fukunaga, and T. Funaki: "A novel transient thermal characterization system for power modules," *IEEE JESTPE*, vol. 13, no. 4, pp. 4955-4964, Aug. 2025.

##### (2) 査読付き国際会議における発表:

3. ○S. Fukunaga, T. Hara, and T. Funaki: "Power variation analysis during transient thermal measurement of semiconductor packages," 2025 International Conference on Electronics Packaging and iMAPS All Asia Conference (ICEP-IAAC2025), TD2-1, Nagano, Japan, Apr. 15-19, 2025. (Oral)

4. ○S. Fukunaga, and T. Funaki: "Challenges of transient thermal characterization for next-generation power semiconductor packages," The 2nd International Symposium on Advanced Power Packaging (ISAPP2025), Fukuoka, Japan, Nov. 5-7, 2025. (Oral, invited)

##### (3) 国内学会等における発表(口頭発表):

5. ○大賀 悠功, 福永 崇平, 舟木 剛: 「金属放熱基板を用いたマルチチップパワーモジュールの熱設計手法に関する一検討 -熱干渉を考慮したチップ配置最適化-」, 電気学会 電子デバイス/半導体電力変換合同研究会, EDD-25-065/SPC-25-197, 金沢商工会議所, 2025年10月23日-24日.